### Development of general purpose low-power small-area 10 bit CMOS DAC

Dominik Przyborowski

April 1, 2009

Dominik Przyborowski Development of general purpose low-power small-area 10

### Outline

- 1 DAC Architecture Overview

- 10 bit Low–Power Small–Area Current–Steering DAC design.

- Specification

- Circuit Design.

- Layout

- 3 1<sup>st</sup> Prototype Measurements Results

- Static Measurements

- Power Measurements

- Transient Measurements

- Comparison with other low-power 10 bit DACs

- Possible Improvements.

- 4 Design of 2<sup>nd</sup> prototype Improvements.

- Oircuit.

- Layout.

### DAC Architecture Overview

#### Nyquist rate DACs architectures:

- charge division,

- resistor strings,

- voltage mode R-2R ladder,

- current mode R-2R ladder,

- current steering.

#### Oversampling DACs:

•  $\Sigma - \Delta$  modulators – not discussed here.

#### Nyquist rate DACs architectures:

- charge division,

- resistor strings,

- voltage mode R-2R ladder,

- current mode R-2R ladder,

- current steering.

#### Oversampling DACs:

•  $\Sigma - \Delta$  modulators – not discussed here.

#### Nyquist rate DACs architectures:

- charge division,

- resistor strings,

- voltage mode R-2R ladder,

- current mode R–2R ladder,

- current steering.

#### Oversampling DACs:

•  $\Sigma - \Delta$  modulators – not discussed here.

#### Nyquist rate DACs architectures:

- charge division,

- resistor strings,

- voltage mode R–2R ladder,

- current mode R–2R ladder,

- current steering.

#### Oversampling DACs:

•  $\Sigma - \Delta$  modulators – not discussed here.

#### Nyquist rate DACs architectures:

- charge division,

- resistor strings,

- voltage mode R-2R ladder,

- current mode R–2R ladder,

- current steering.

#### Oversampling DACs:

•  $\Sigma - \Delta$  modulators – not discussed here.

#### Nyquist rate DACs architectures:

- charge division,

- resistor strings,

- voltage mode R–2R ladder,

- current mode R–2R ladder,

- current steering.

#### Oversampling DACs:

•  $\Sigma - \Delta$  modulators – not discussed here.

A = A A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

#### Nyquist rate DACs architectures:

- charge division,

- resistor strings,

- voltage mode R–2R ladder,

- current mode R–2R ladder,

- current steering.

#### Oversampling DACs:

•  $\Sigma - \Delta$  modulators – not discussed here.

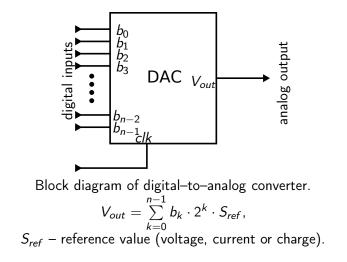

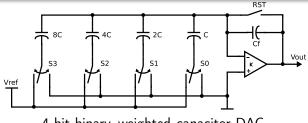

# DAC Architecture Overview Charge Division.

4 bit binary-weighted capacitor DAC.

Properties

$$V_{out} = -rac{C}{C_f} \cdot \sum_{k=0}^{N-1} 2^k \cdot S_k \cdot V_{ref}$$

Dominik Przyborowski Development of general purpose low-power small-area 10

# DAC Architecture Overview Charge Division.

4 bit binary-weighted capacitor DAC.

#### Properties

$$V_{out} = -rac{C}{C_f} \cdot \sum_{k=0}^{N-1} 2^k \cdot S_k \cdot V_{ref}$$

- resolution up to 12 bits,

- low DC power consumption (only Op Amp and digital part)

- ullet requires refreshing (capacitors leakage current is  $pprox \; 1 a A$

# DAC Architecture Overview Charge Division.

4 bit binary-weighted capacitor DAC.

#### Properties

$$V_{out} = -rac{C}{C_f} \cdot \sum_{k=0}^{N-1} 2^k \cdot S_k \cdot V_{ref}$$

- resolution up to 12 bits,

- low DC power consumption (only Op Amp and digital part)

- ullet requires refreshing (capacitors leakage current is  $pprox \; 1$ aA

# DAC Architecture Overview Charge Division.

4 bit binary-weighted capacitor DAC.

#### Properties

$$V_{out} = -rac{C}{C_f} \cdot \sum_{k=0}^{N-1} 2^k \cdot S_k \cdot V_{ref}$$

- resolution up to 12 bits,

- low DC power consumption (only Op Amp and digital part)

- requires refreshing (capacitors leakage current is  $\approx~1aA$ )

#### DAC Architecture Overview Resistor String.

3 bit resistor string DAC.

A = A A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

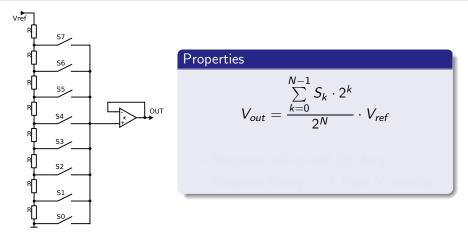

# DAC Architecture Overview Resistor String.

Properties

3 bit resistor string DAC.

# $V_{out} = \frac{\sum_{k=0}^{N-1} S_k \cdot 2^k}{2^N} \cdot V_{ref}$ • Requires rail-to-rail Op Amp. • Requires *binary* $\rightarrow 1$ from N decoder.

伺き イヨト イヨト

# DAC Architecture Overview Resistor String.

3 bit resistor string DAC.

#### Properties

$$V_{out} = \frac{\sum\limits_{k=0}^{N-1} S_k \cdot 2^k}{2^N} \cdot V_{ref}$$

- Requires rail-to-rail Op Amp.

- Requires *binary*  $\rightarrow$  1 *from* N decoder.

A = A A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

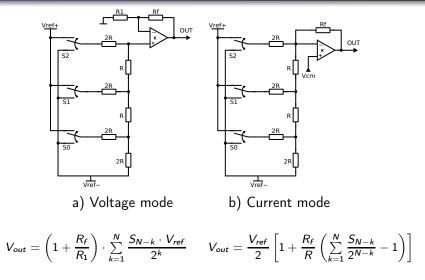

#### DAC Architecture Overview Resistor R–2R Ladder.

• • = • • = •

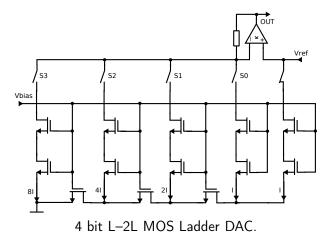

#### DAC Architecture Overview Resistor R-2R Ladder – MOS implementation I.

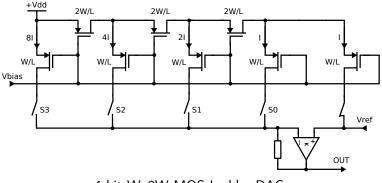

#### DAC Architecture Overview Resistor R–2R Ladder – MOS implementation II.

4 bit W-2W MOS Ladder DAC.

#### DAC Architecture Overview Resistor R–2R Ladder – MOS implementation III.

#### M-2M mismatch considerations

- In M–2M network transistors in different operational points.

- Matching in saturation region is determined by overdrive voltage:

$$\sigma(I_d) = \sqrt{\frac{A_{\beta}^2}{W \cdot L} + \left(\frac{2 \cdot 100\% \cdot A_{V_{th}}}{V_{ov}}\right)^2 \cdot \frac{1}{W \cdot L}}$$

Matching of MOS transistors in triode region is affected by output opamp offset:

$$\sigma(I_d) = \sqrt{\frac{A_{\beta}^2}{W \cdot L} + \left(\frac{100\% \cdot A_{V_{th}}}{V_{ov} - \frac{1}{2}V_{ds}}\right)^2 \cdot \frac{1}{W \cdot L} + \left(100\% \cdot \frac{\Delta V_{ds}}{V_{ds}}\right)^2}$$

• Simulations results required *special care* – problem with discontinuities of the BSIM transistors model.

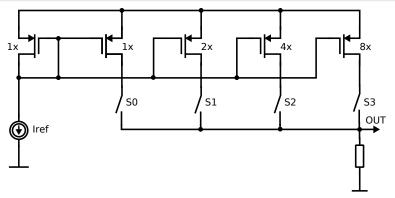

# DAC Architecture Overview Current Steering.

4 bit Current Steering DAC.

$$V_{out} = I_{ref} \cdot R \cdot \sum_{K=0}^{N-1} S_k \cdot 2^k$$

### Outline

#### DAC Architecture Overview

- 2 10 bit Low–Power Small–Area Current–Steering DAC design.

Specification

- Circuit Design.

- Layout

- 3 1<sup>st</sup> Prototype Measurements Results

- Static Measurements

- Power Measurements

- Transient Measurements

- Comparison with other low-power 10 bit DACs

- Possible Improvements.

- 4 Design of 2<sup>nd</sup> prototype Improvements.

- Circuit.

- Layout.

A B A A B

#### Requirements:

- 10 bit resolution.

- High swing voltage output.

- Low power consumption below 1 [mW].

- Small area.

#### Considered architectures:

- Current steering

- Resistors ladder.

#### Chosen architecture:

Current steering – matching of MOS better than resistors

#### Requirements:

- 10 bit resolution.

- High swing voltage output.

- Low power consumption below 1 [mW].

- Small area.

#### Considered architectures:

- Current steering

- Resistors ladder.

#### Chosen architecture:

Current steering – matching of MOS better than resistors.

#### Requirements:

- 10 bit resolution.

- High swing voltage output.

- Low power consumption below 1 [mW].

#### Small area.

#### Considered architectures:

- Current steering

- Resistors ladder.

#### Chosen architecture:

Current steering – matching of MOS better than resistors

#### Requirements:

- 10 bit resolution.

- High swing voltage output.

- Low power consumption below 1 [mW].

#### Small area.

#### Considered architectures:

- Current steering

- Resistors ladder.

#### Chosen architecture:

Current steering – matching of MOS better than resistors

#### Requirements:

- 10 bit resolution.

- High swing voltage output.

- Low power consumption below 1 [mW].

- Small area.

#### Considered architectures:

- Current steering

- Resistors ladder.

#### Chosen architecture:

Current steering – matching of MOS better than resistors

A (1) > A (1) > A

#### Requirements:

- 10 bit resolution.

- High swing voltage output.

- Low power consumption below 1 [mW].

- Small area.

#### Considered architectures:

- Current steering.

- Resistors ladder.

#### Chosen architecture:

Current steering – matching of MOS better than resistors

#### Requirements:

- 10 bit resolution.

- High swing voltage output.

- Low power consumption below 1 [mW].

- Small area.

#### Considered architectures:

- Current steering.

- Resistors ladder.

#### Chosen architecture:

Current steering – matching of MOS better than resistors

#### Requirements:

- 10 bit resolution.

- High swing voltage output.

- Low power consumption below 1 [mW].

- Small area.

#### Considered architectures:

- Current steering.

- Resistors ladder.

#### Chosen architecture:

Current steering – matching of MOS better than resistors.

### Outline

#### DAC Architecture Overview

# 2 10 bit Low–Power Small–Area Current–Steering DAC design. Specification

- Circuit Design.

- Layout

- 3 1<sup>st</sup> Prototype Measurements Results

- Static Measurements

- Power Measurements

- Transient Measurements

- Comparison with other low-power 10 bit DACs

- Possible Improvements.

- 4 Design of 2<sup>nd</sup> prototype Improvements.

- Circuit.

- Layout.

A B A A B

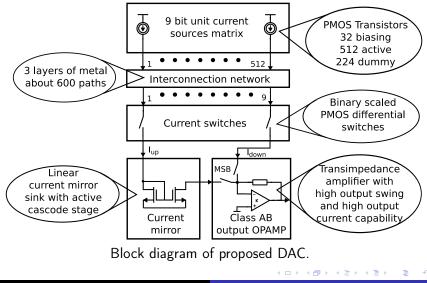

#### 10 bit Low–Power Small–Area Current–Steering DAC design. Circuit Design.

Dominik Przyborowski Development of general purpose low-power small-area 10 l

10 bit Low–Power Small–Area Current–Steering DAC design. Circuit Design – 9 bit Current Sources Array I.

Require for 9 bit resolution:

$$\delta I_{MSB} \le \frac{1}{3} \cdot 2^{-9} \cdot 100\% = 0.065\%$$

formulas for calculating dimensions:  $\frac{W}{L} = \frac{2 \cdot I_D}{\beta \cdot V_{ov}^2}, \qquad \beta = \mu_0 \cdot C_{ox}$   $W \cdot L \ge \frac{1}{\sigma^2(I_D)} \cdot \left[A_{\beta}^2 + \left(\frac{2 \cdot A_{V_{th}}}{V_{out}} \cdot 100\%\right)^2\right]$

Mismatch parameters in used technology:

NMOS:  $A_{\beta} = 0.2 \ [\mu m \cdot \%]$   $A_{V_{th}} = 8.2 \ [\mu m \cdot mV]$ PMOS:  $A_{\beta} = 0.4 \ [\mu m \cdot \%]$   $A_{V_{th}} = 14.9 \ [\mu m \cdot mV]$

Dominik Przyborowski Development of general purpose low-power small-area 10

Arch. Overview DAC Design Measurements New Design Assumptions Overview Layout

10 bit Low–Power Small–Area Current–Steering DAC design. Circuit Design – 9 bit Current Sources Array I.

Require for 9 bit resolution:

$$\delta I_{MSB} \le rac{1}{3} \cdot 2^{-9} \cdot 100\% = 0.065\%$$

Formulas for calculating dimensions:

$$\frac{W}{L} = \frac{2 \cdot I_D}{\beta \cdot V_{ov}^2}, \qquad \beta = \mu_0 \cdot C_{ox}$$

$$W \cdot L \ge \frac{1}{\sigma^2(I_D)} \cdot \left[ A_{\beta}^2 + \left( \frac{2 \cdot A_{V_{th}}}{V_{ov}} \cdot 100\% \right)^2 \right]$$

Mismatch parameters in used technology:

NMOS:

$$A_{\beta} = 0.2 \ [\mu m \cdot \%]$$

$A_{V_{th}} = 8.2 \ [\mu m \cdot mV]$

PMOS:  $A_{\beta} = 0.4 \ [\mu m \cdot \%]$   $A_{V_{th}} = 14.9 \ [\mu m \cdot mV]$

Dominik Przyborowski Development of general purpose low-power small-area 10

Arch. Overview DAC Design Measurements New Design Assumptions Overview Layout

10 bit Low–Power Small–Area Current–Steering DAC design. Circuit Design – 9 bit Current Sources Array I.

Require for 9 bit resolution:

$$\delta I_{MSB} \le rac{1}{3} \cdot 2^{-9} \cdot 100\% = 0.065\%$$

Formulas for calculating dimensions:

$$\frac{W}{L} = \frac{2 \cdot I_D}{\beta \cdot V_{ov}^2}, \qquad \beta = \mu_0 \cdot C_{ox}$$

$$W \cdot L \ge \frac{1}{\sigma^2(I_D)} \cdot \left[ A_\beta^2 + \left( \frac{2 \cdot A_{V_{th}}}{V_{ov}} \cdot 100\% \right)^2 \right]$$

Mismatch parameters in used technology:

NMOS:

$$A_{\beta} = 0.2 \ [\mu m \cdot \%]$$

$A_{V_{th}} = 8.2 \ [\mu m \cdot mV]$

PMOS:  $A_{\beta} = 0.4 \ [\mu m \cdot \%]$   $A_{V_{th}} = 14.9 \ [\mu m \cdot mV]$

Dominik Przyborowski Development of general purpose low-power small-area 10

・ロト ・ 同ト ・ ヨト ・ ヨト

### Choice of transistors size:

- Assumed LSB current = 100[nA]

- Assumed current source overdrive voltage  $\geq 500[mV]$

- Chosen transistor type PMOS

- Chosen W/L unit transistor ratio 1/80 ( $V_{ov} = 637[mV]$ )

- Calculated unit current source dimensions  $0.5\mu/40\mu$

#### Choice of transistors size:

- Assumed LSB current = 100[nA]

- Assumed current source overdrive voltage  $\geq 500[mV]$

- Chosen transistor type PMOS

- Chosen W/L unit transistor ratio 1/80 (V<sub>ov</sub> = 637[mV])

- Calculated unit current source dimensions  $0.5\mu/40\mu$

#### Choice of transistors size:

- Assumed LSB current = 100[nA]

- Assumed current source overdrive voltage  $\geq 500[mV]$

- Chosen transistor type PMOS

- Chosen W/L unit transistor ratio 1/80 ( $V_{ov} = 637[mV]$ )

- Calculated unit current source dimensions  $0.5\mu/40\mu$

#### Choice of transistors size:

- Assumed LSB current = 100[nA]

- Assumed current source overdrive voltage  $\geq 500[mV]$

- Chosen transistor type PMOS

- Chosen W/L unit transistor ratio  $-1/80 (V_{ov} = 637[mV])$

- Calculated unit current source dimensions  $0.5\mu/40\mu$

A > < > < >

### Choice of transistors size:

- Assumed LSB current = 100[nA]

- Assumed current source overdrive voltage  $\geq 500[mV]$

- Chosen transistor type PMOS

- Chosen W/L unit transistor ratio  $-1/80 (V_{ov} = 637[mV])$

- Calculated unit current source dimensions  $0.5\mu/40\mu$

▲ □ ▶ ▲ □ ▶ ▲ □ ▶

### Choice of transistors size:

- Assumed LSB current = 100[nA]

- Assumed current source overdrive voltage  $\geq 500[mV]$

- Chosen transistor type PMOS

- Chosen W/L unit transistor ratio 1/80 (V<sub>ov</sub> = 637[mV])

- $\bullet\,$  Calculated unit current source dimensions  $0.5\mu/40\mu$

Arch. Overview DAC Design Measurements New Design Assumptions Overview Layout

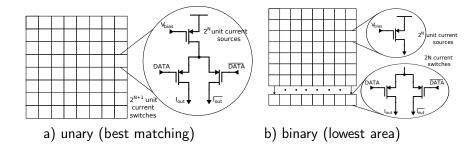

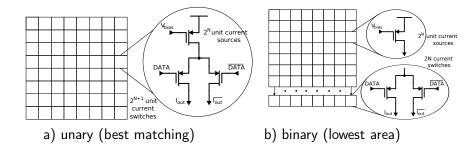

### 10 bit Low–Power Small–Area Current–Steering DAC design. Circuit Design – Current Switches.

#### Current switches – conclusion

To minimize area binary switching (b) was chosen. Dimensions of LSB switch –  $0.4\mu/0.35\mu$ .

### 10 bit Low–Power Small–Area Current–Steering DAC design. Circuit Design – Current Switches.

#### Current switches - conclusion

To minimize area binary switching (b) was chosen. Dimensions of LSB switch –  $0.4\mu/0.35\mu$ .

< 6 >

Arch. Overview DAC Design Measurements New Design Assumptions Overview Layout

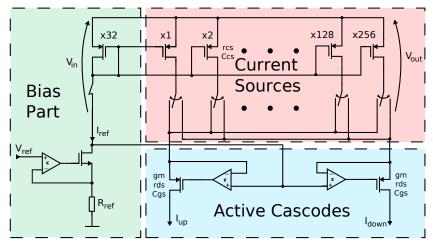

10 bit Low–Power Small–Area Current–Steering DAC design. Circuit Design – Current Source Array with Active Cascodes Stage.

Bias circuit, current sources array and active cascode stage.

#### Advantages of active cascodes:

- Drain current independent from channel modulation factor.

- Strongly increases output resistance:

$$r_{out}\simeq K\cdot g_{m}\cdot r_{ds}\cdot r_{CS}pprox 10^{14}\div 10^{16}\Omega$$

• Glitch reduction.

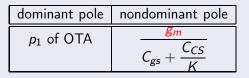

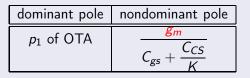

## Possibles problems:

Stability

# Needs minimum current!

Dominik Przyborowski Development of general purpose low-power small-area 10

#### Advantages of active cascodes:

- Drain current independent from channel modulation factor.

- Strongly increases output resistance:  $r_{out} \simeq K \cdot g_m \cdot r_{ds} \cdot r_{CS} \approx 10^{14} \div 10^{14}$

- Glitch reduction.

### Possibles problems:

Stability

# Needs minimum current!

Dominik Przyborowski Development of general purpose low-power small-area 10

イロト イポト イヨト イヨト

#### Advantages of active cascodes:

- Drain current independent from channel modulation factor.

- Strongly increases output resistance:

$$r_{out} \simeq K \cdot g_m \cdot r_{ds} \cdot r_{CS} \approx 10^{14} \div 10^{16} \Omega$$

• Glitch reduction.

#### Advantages of active cascodes:

- Drain current independent from channel modulation factor.

- Strongly increases output resistance:

$$r_{out} \simeq K \cdot g_m \cdot r_{ds} \cdot r_{CS} \approx 10^{14} \div 10^{16} \Omega$$

Glitch reduction.

Dominik Przyborowski Development of general purpose low-power small-area 10

### Advantages of active cascodes:

- Drain current independent from channel modulation factor.

- Strongly increases output resistance:

$$r_{out} \simeq K \cdot g_m \cdot r_{ds} \cdot r_{CS} \approx 10^{14} \div 10^{16} \Omega$$

Glitch reduction.

### Possibles problems:

Stability

Needs minimum current!

Dominik Przyborowski Development of general purpose low-power small-area 10

### Advantages of active cascodes:

- Drain current independent from channel modulation factor.

- Strongly increases output resistance:

$$r_{out} \simeq K \cdot g_m \cdot r_{ds} \cdot r_{CS} \approx 10^{14} \div 10^{16} \Omega$$

Glitch reduction.

### Possibles problems:

Stability

Needs minimum current!

Dominik Przyborowski Development of general purpose low-power small-area 10

Arch. Overview DAC Design Measurements New Design Assumptions Overview Layout

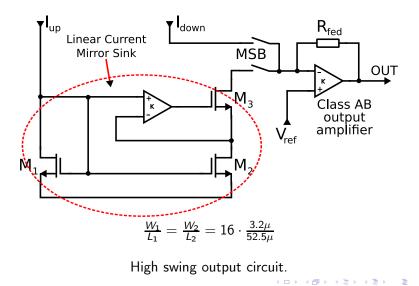

10 bit Low–Power Small–Area Current–Steering DAC design. Circuit Design – High Swing Output Stage (Including Current Mirror Sink) I.

10 bit Low–Power Small–Area Current–Steering DAC design. Circuit Design – High Swing Output Stage II.

Relation between *I*<sub>down</sub> and *I*<sub>up</sub>:

$$I_{down} = 511 \cdot I_{LSB} - B_{dec} \cdot I_{up}$$

$B_{dec}$  – decimal representation of input word (without MSB bit).

### Output voltage:

• MSB = 0:  $V_{out} = V_{ref} - (511 - B_{dec}) \cdot I_{LSB} \cdot R_{fec}$ • MSB = 1:  $V_{out} = V_{ref} + B_{dec} \cdot I_{LSB} \cdot R_{fed}$

伺き イヨト イヨト

10 bit Low–Power Small–Area Current–Steering DAC design. Circuit Design – High Swing Output Stage II.

Relation between  $I_{down}$  and  $\overline{I_{up}}$ :

$$I_{down} = 511 \cdot I_{LSB} - B_{dec} \cdot I_{up}$$

$B_{dec}$  – decimal representation of input word (without MSB bit).

### Output voltage:

• MSB = 0:

$$V_{out} = V_{ref} - (511 - B_{dec}) \cdot I_{LSB} \cdot R_{fed}$$

• MSB = 1:  $V_{out} = V_{ref} + B_{dec} \cdot I_{LSB} \cdot R_{fed}$

・ 同 ト ・ ヨ ト ・ ヨ ト

10 bit Low–Power Small–Area Current–Steering DAC design. Circuit Design – High Swing Output Stage II.

Relation between  $I_{down}$  and  $\overline{I_{up}}$ :

$$I_{down} = 511 \cdot I_{LSB} - B_{dec} \cdot I_{up}$$

$B_{dec}$  – decimal representation of input word (without MSB bit).

### Output voltage:

• MSB = 0:

$$V_{out} = V_{ref} - (511 - B_{dec}) \cdot I_{LSB} \cdot R_{fed}$$

• MSB = 1:

$$V_{out} = V_{ref} + B_{dec} \cdot I_{LSB} \cdot R_{fed}$$

#### Two types of amplifiers were used:

- Single stage OTAs in active cascode stages and biasing. Depending on voltage level OTA use either NMOS or PMOS input differential pair.

- Two stage class AB operational amplifier for output current-to-voltage converter.

### Single stage OTA – details:

- Architecture folded cascode.

- Power consumption [µW] 3.5 (NMOS), 25 (PMOS).

- Open loop Gain [dB] 60 (NMOS), 88 (PMOS).

- Gain x Bandwidth (GBW) [MHz] 1 (NMOS), 7 (PMOS).

- Phase Margin > 70°.

#### Two types of amplifiers were used:

- Single stage OTAs in active cascode stages and biasing. Depending on voltage level OTA use either NMOS or PMOS input differential pair.

- Two stage class AB operational amplifier for output current-to-voltage converter.

### Single stage OTA – details:

- Architecture folded cascode.

- Power consumption  $[\mu W] 3.5$  (NMOS), 25 (PMOS).

- Open loop Gain [dB] 60 (NMOS), 88 (PMOS).

- Gain x Bandwidth (GBW) [MHz] 1 (NMOS), 7 (PMOS).

- Phase Margin  $> 70^{\circ}$ .

#### Two types of amplifiers were used:

- Single stage OTAs in active cascode stages and biasing. Depending on voltage level OTA use either NMOS or PMOS input differential pair.

- Two stage class AB operational amplifier for output current-to-voltage converter.

### Single stage OTA – details:

- Architecture folded cascode.

- Power consumption  $[\mu W] 3.5$  (NMOS), 25 (PMOS).

- Open loop Gain [dB] 60 (NMOS), 88 (PMOS).

- Gain x Bandwidth (GBW) [MHz] 1 (NMOS), 7 (PMOS).

- Phase Margin > 70°.

#### Two types of amplifiers were used:

- Single stage OTAs in active cascode stages and biasing. Depending on voltage level OTA use either NMOS or PMOS input differential pair.

- Two stage class AB operational amplifier for output current-to-voltage converter.

### Single stage OTA – details:

- Architecture folded cascode.

- Power consumption  $[\mu W] 3.5$  (NMOS), 25 (PMOS).

- Open loop Gain [dB] 60 (NMOS), 88 (PMOS).

- Gain x Bandwidth (GBW) [MHz] 1 (NMOS), 7 (PMOS).

- Phase Margin > 70°.

#### Two types of amplifiers were used:

- Single stage OTAs in active cascode stages and biasing. Depending on voltage level OTA use either NMOS or PMOS input differential pair.

- Two stage class AB operational amplifier for output current-to-voltage converter.

### Single stage OTA – details:

- Architecture folded cascode.

- Power consumption  $[\mu W] 3.5$  (NMOS), 25 (PMOS).

- Open loop Gain [dB] 60 (NMOS), 88 (PMOS).

- Gain x Bandwidth (GBW) [MHz] 1 (NMOS), 7 (PMOS).

- Phase Margin  $> 70^{\circ}$ .

#### Two types of amplifiers were used:

- Single stage OTAs in active cascode stages and biasing. Depending on voltage level OTA use either NMOS or PMOS input differential pair.

- Two stage class AB operational amplifier for output current-to-voltage converter.

### Single stage OTA – details:

- Architecture folded cascode.

- Power consumption  $[\mu W] 3.5$  (NMOS), 25 (PMOS).

- Open loop Gain [dB] 60 (NMOS), 88 (PMOS).

- Gain x Bandwidth (GBW) [MHz] 1 (NMOS), 7 (PMOS).

- Phase Margin > 70°.

Arch. Overview DAC Design Measurements New Design Assumptions Overview Layout

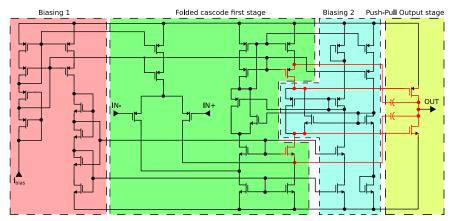

### 10 bit Low–Power Small–Area Current–Steering DAC design. Circuit Design – Class AB Operational Amplifier I.

Schematic of output class AB operational amplifier.

— Cascoded Miller compensation.

## Class AB OP-AMP:

- Sooch cascode current mirror used for biasing.

- 1<sup>st</sup> stage build as a folded cascode.

- Bias of Push–Pull output stage designed as *floating current source*.

- Push–Pull output stage with cascoded Miller compensation technique.

- Better PSRR (Power Supply Rejection Ratio).

- 🖌 Needs 2–3 times smaller comp. cap. (wider bandwidth).

- Doesn't require resistor.

- X Complicated transfer function 3 poles and 2 zeros (problems with high frequency gain peak).

### Class AB OP-AMP:

- Sooch cascode current mirror used for biasing.

- 1<sup>st</sup> stage build as a folded cascode.

- Bias of Push–Pull output stage designed as *floating current source*.

- Push–Pull output stage with cascoded Miller compensation technique.

- Better PSRR (Power Supply Rejection Ratio).

- Needs 2–3 times smaller comp. cap. (wider bandwidth).

- Doesn't require resistor.

- X Complicated transfer function 3 poles and 2 zeros (problems with high frequency gain peak).

### Class AB OP-AMP:

- Sooch cascode current mirror used for biasing.

- 1<sup>st</sup> stage build as a folded cascode.

- Bias of Push–Pull output stage designed as *floating current source*.

- Push–Pull output stage with cascoded Miller compensation technique.

- Better PSRR (Power Supply Rejection Ratio).

- 🖌 Needs 2–3 times smaller comp. cap. (wider bandwidth).

- Doesn't require resistor.

- X Complicated transfer function 3 poles and 2 zeros (problems with high frequency gain peak).

### Class AB OP-AMP:

- Sooch cascode current mirror used for biasing.

- 1<sup>st</sup> stage build as a folded cascode.

- Bias of Push–Pull output stage designed as *floating current source*.

- Push–Pull output stage with cascoded Miller compensation technique.

- Better PSRR (Power Supply Rejection Ratio).

- 🖌 Needs 2–3 times smaller comp. cap. (wider bandwidth).

- Doesn't require resistor.

- X Complicated transfer function 3 poles and 2 zeros (problems with high frequency gain peak).

### Class AB OP-AMP:

- Sooch cascode current mirror used for biasing.

- 1<sup>st</sup> stage build as a folded cascode.

- Bias of Push–Pull output stage designed as *floating current source*.

- Push–Pull output stage with cascoded Miller compensation technique.

- Better PSRR (Power Supply Rejection Ratio).

- Needs 2–3 times smaller comp. cap. (wider bandwidth).

- Doesn't require resistor.

- X Complicated transfer function 3 poles and 2 zeros (problems with high frequency gain peak).

### Class AB OP-AMP:

- Sooch cascode current mirror used for biasing.

- 1<sup>st</sup> stage build as a folded cascode.

- Bias of Push–Pull output stage designed as *floating current source*.

- Push–Pull output stage with cascoded Miller compensation technique.

- Better PSRR (Power Supply Rejection Ratio).

- Needs 2–3 times smaller comp. cap. (wider bandwidth).

- Doesn't require resistor.

- Complicated transfer function 3 poles and 2 zeros (problems with high frequency gain peak).

### Class AB OP-AMP:

- Sooch cascode current mirror used for biasing.

- 1<sup>st</sup> stage build as a folded cascode.

- Bias of Push–Pull output stage designed as *floating current source*.

- Push–Pull output stage with cascoded Miller compensation technique.

- ✓ Better PSRR (Power Supply Rejection Ratio).

- Needs 2–3 times smaller comp. cap. (wider bandwidth).

- Doesn't require resistor.

- Complicated transfer function 3 poles and 2 zeros (problems with high frequency gain peak).

### Class AB OP-AMP:

- Sooch cascode current mirror used for biasing.

- 1<sup>st</sup> stage build as a folded cascode.

- Bias of Push–Pull output stage designed as *floating current source*.

- Push–Pull output stage with cascoded Miller compensation technique.

#### Cascoded Miller compensation technique pros and cons:

- ✓ Better PSRR (Power Supply Rejection Ratio).

- ✓ Needs 2–3 times smaller comp. cap. (wider bandwidth).

- Doesn't require resistor.

Complicated transfer function – 3 poles and 2 zeros (problems with high frequency gain peak).

### Class AB OP-AMP:

- Sooch cascode current mirror used for biasing.

- 1<sup>st</sup> stage build as a folded cascode.

- Bias of Push–Pull output stage designed as *floating current source*.

- Push–Pull output stage with cascoded Miller compensation technique.

- ✓ Better PSRR (Power Supply Rejection Ratio).

- ✓ Needs 2–3 times smaller comp. cap. (wider bandwidth).

- Doesn't require resistor.

- Complicated transfer function 3 poles and 2 zeros (problems with high frequency gain peak).

### Class AB OP-AMP:

- Sooch cascode current mirror used for biasing.

- 1<sup>st</sup> stage build as a folded cascode.

- Bias of Push–Pull output stage designed as *floating current source*.

- Push–Pull output stage with cascoded Miller compensation technique.

- ✓ Better PSRR (Power Supply Rejection Ratio).

- ✓ Needs 2–3 times smaller comp. cap. (wider bandwidth).

- Doesn't require resistor.

- Complicated transfer function 3 poles and 2 zeros (problems with high frequency gain peak).

#### Class AB OP-AMP parameters:

- Power consumption 65  $\mu W (+V_{dd} \cdot I_{out})$ .

- Open loop gain 115 dB (for zero current load)

- GBW 2 MHz

- Phase Margin  $> 75^{\circ}$ .

• • = • • =

- Power consumption 65  $\mu W (+V_{dd} \cdot I_{out})$ .

- Open loop gain 115 dB (for zero current load)

- GBW 2 MHz

- Phase Margin  $> 75^{\circ}$ .

- Power consumption 65  $\mu W (+V_{dd} \cdot I_{out})$ .

- Open loop gain 115 dB (for zero current load)

- GBW 2 MHz

- Phase Margin  $> 75^{\circ}$ .

- Power consumption 65  $\mu W (+V_{dd} \cdot I_{out})$ .

- Open loop gain 115 dB (for zero current load)

- GBW 2 MHz

- Phase Margin  $> 75^{\circ}$ .

- Power consumption 65  $\mu W (+V_{dd} \cdot I_{out})$ .

- Open loop gain 115 dB (for zero current load)

- GBW 2 MHz

- Phase Margin  $> 75^{\circ}$ .

### DAC Architecture Overview

### 10 bit Low–Power Small–Area Current–Steering DAC design.

- Specification

- Circuit Design.

#### Layout

- 3 1<sup>st</sup> Prototype Measurements Results

- Static Measurements

- Power Measurements

- Transient Measurements

- Comparison with other low-power 10 bit DACs

- Possible Improvements.

- 4 Design of 2<sup>nd</sup> prototype Improvements.

- Circuit.

- Layout.

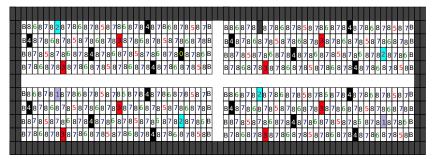

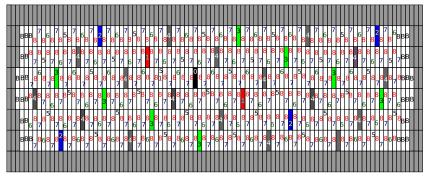

#### Layout 9 bit Current Sources Array.

### Block Diagram of DAC Matrix Layout.

-

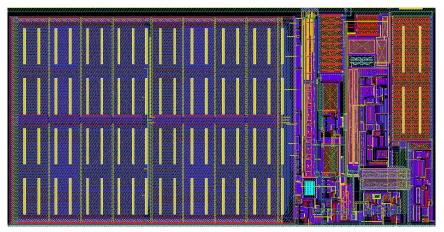

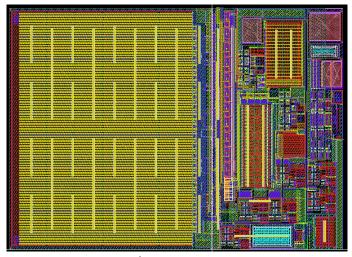

#### Layout DAC Core.

Layout of  $1^{st}$  prototype (295x595 $\mu$ m).

### DAC Architecture Overview

- 2 10 bit Low–Power Small–Area Current–Steering DAC design.

- Specification

- Circuit Design.

- Layout

### 3 1<sup>st</sup> Prototype Measurements Results

### Static Measurements

- Power Measurements

- Transient Measurements

- Comparison with other low-power 10 bit DACs

- Possible Improvements.

- 4 Design of 2<sup>nd</sup> prototype Improvements.

- Circuit.

- Layout.

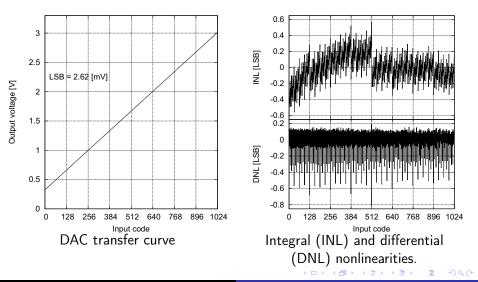

### 1<sup>st</sup> Prototype Measurements Results Static Measurements I.

### 1<sup>st</sup> Prototype Measurements Results Static Measurements II.

|                 | Channel no             | 1    | 2    | 3    | 4    | 5    |

|-----------------|------------------------|------|------|------|------|------|

| b.              | LSB value [mV]         | 2.62 | 2.59 | 2.62 | 2.64 | 2.68 |

| chip            | max.  INL  [LSB]       | 0.65 | 0.75 | 0.6  | 0.6  | 0.65 |

| 1 <sup>st</sup> | max.  DNL  [LSB]       | 1.1  | 0.9  | 1.1  | 0.9  | 1.05 |

|                 | Codes of $ DNL  > 0.5$ | 13   | 17   | 14   | 8    | 26   |

|                 | Nr of missing values   | 4    | 0    | 2    | 0    | 3    |

|                 | Channel no             | 1    | 2    | 3    | 4    | 5    |

| chip            | LSB value [mV]         | 2.58 | 2.59 | 2.62 | 2.61 | 2.63 |

| ch              | max.  INL  [LSB]       | 0.45 | 0.5  | 0.6  | 0.6  | 0.7  |

| 2 <sup>nd</sup> | max.  DNL  [LSB]       | 0.75 | 0.95 | 0.8  | 0.7  | 1.2  |

|                 | Codes of $ DNL  > 0.5$ | 15   | 2    | 29   | 22   | 20   |

|                 | Nr of missing values   | 0    | 2    | 0    | 0    | 2    |

A B M A B M

### DAC Architecture Overview

- 2 10 bit Low–Power Small–Area Current–Steering DAC design.

- Specification

- Circuit Design.

- Layout

### 3 1<sup>st</sup> Prototype Measurements Results

- Static Measurements

- Power Measurements

- Transient Measurements

- Comparison with other low-power 10 bit DACs

- Possible Improvements.

- 4 Design of 2<sup>nd</sup> prototype Improvements.

- Circuit.

- Layout.

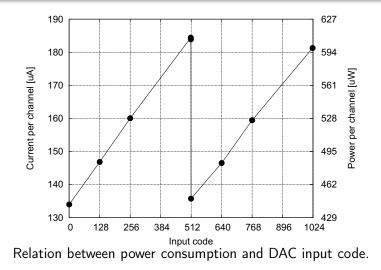

### 1<sup>st</sup> Prototype Measurements Results Power Measurements

### DAC Architecture Overview

- 2 10 bit Low–Power Small–Area Current–Steering DAC design.

- Specification

- Circuit Design.

- Layout

### 3 1<sup>st</sup> Prototype Measurements Results

- Static Measurements

- Power Measurements

- Transient Measurements

- Comparison with other low-power 10 bit DACs

- Possible Improvements.

- Obsign of 2<sup>nd</sup> prototype Improvements.

- Circuit.

- Layout.

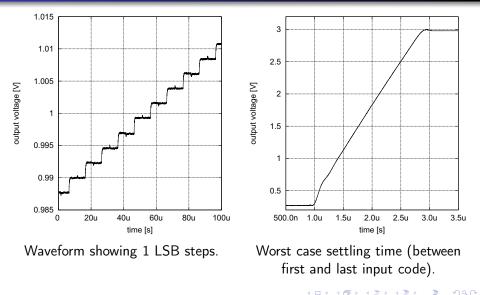

#### 1<sup>st</sup> Prototype Measurements Results Transient Measurements.

### DAC Architecture Overview

- 2 10 bit Low–Power Small–Area Current–Steering DAC design.

- Specification

- Circuit Design.

- Layout

### 3 1<sup>st</sup> Prototype Measurements Results

- Static Measurements

- Power Measurements

- Transient Measurements

• Comparison with other low-power 10 bit DACs

• Possible Improvements.

4 Design of 2<sup>nd</sup> prototype – Improvements.

- Circuit.

- Layout.

|                            | 1                    | 2                 | 3                                                                 | 4                     | This work                                         |

|----------------------------|----------------------|-------------------|-------------------------------------------------------------------|-----------------------|---------------------------------------------------|

| architecture               | current<br>steering  | R–2R<br>ladder    | resistor<br>ladder                                                | resistor<br>string    | current<br>steering                               |

| technology                 | 0.35 μm<br>CMOS      | 0.18 μm<br>CMOS   | 0.35 μm<br>CMOS                                                   | 0.13 μm<br>CMOS       | 0.35 μm<br>CMOS                                   |

| power<br>cons. [mW]        | <b>≤ 7.8</b>         | 4                 | 0.07<br>(analog part)                                             | 0.5                   | $\leq$ 0.6                                        |

| area<br>[mm <sup>2</sup> ] | 0.23                 | 0.01              | 0.022                                                             | 0.18                  | 0.18                                              |

| max INL<br>[LSB]           | 0.2                  | 0.75              | 0.7                                                               | 2.0                   | 0.6                                               |

| max DNL<br>[LSB]           | 0.2                  | 0.7               | 0.35                                                              | 0.5                   | 0.8                                               |

| speed                      | upd. rate<br>30 MS/s | low<br>frequency  | set. time<br>3 $\mu s/10  m  m  m  m  m  m  m  m  m  m  m  m  m $ | upd. rate<br>2MS/s    | worst $t_{set}$ 2 $\mu s$<br>1 LSB $t_r$ < 500 ns |

| output<br>type             | current<br>≤2.5mA    | current<br><2.2mA | voltage<br>without buffer                                         | voltage<br>high–swing | voltage<br>high–swing                             |

Comparison with other low-power 10 bit DACs

- 1 M. Borremans, A. Van den Bosch, M. Steyeart, W. Sansen, A low power 10-bit CMOS D/A converter for high speed applications, IEEE 2001 custom integrated circuits conference.

- 2 B. Greenlay, R. Veith, Dong-Young Chang, Un-Ku Moon, A low-voltage 10-bit CMOS DAC in 0.01-mm<sup>2</sup> die area, IEEE Transactions on Circuits and Systems, vol. 52, no 5, 2005.

- 3 Y. Perelman, R. Ginosar, A low-power inverted ladder D/A converter, IEEE Transactions on Circuits and Systems, vol. 53, no 6, 2006.

- 4 F. Ge, M. Trivedi, B. Thomas, W. Jiang, H. Song, 1.5V 0.5mW 2MSPS 10B DAC with rail-to-rail output in 0.13μm CMOS technology, SOC Conference, 2008/IEEE International. ≣ → Ω < <

### DAC Architecture Overview

- 2 10 bit Low–Power Small–Area Current–Steering DAC design.

- Specification

- Circuit Design.

- Layout

### 3 1<sup>st</sup> Prototype Measurements Results

- Static Measurements

- Power Measurements

- Transient Measurements

- Comparison with other low-power 10 bit DACs

- Possible Improvements.

- 4 Design of 2<sup>nd</sup> prototype Improvements.

- Circuit.

- Layout.

### Possible Improvements.

### What is not good:

- DNL higher than expected (over 0.5 LSB). Some missing values.

- Asymmetry of rise time for outputs signals input code with MSB = 1 and MSB = 0.

### Solutions:

- Layout of current source matrix to be improved.

- Large time constant of linear current mirror sink.

伺き イヨト イヨト

### Possible Improvements.

#### What is not good:

- DNL higher than expected (over 0.5 LSB). Some missing values.

- Asymmetry of rise time for outputs signals input code with MSB = 1 and MSB = 0.

#### Solutions:

- Layout of current source matrix to be improved.

- Large time constant of linear current mirror sink.

### Possible Improvements.

#### What is not good:

- DNL higher than expected (over 0.5 LSB). Some missing values.

- Asymmetry of rise time for outputs signals input code with MSB = 1 and MSB = 0.

### Solutions:

- Layout of current source matrix to be improved.

- Large time constant of linear current mirror sink.

- DAC Architecture Overview

- 2 10 bit Low–Power Small–Area Current–Steering DAC design.

- Specification

- Circuit Design.

- Layout

- 3 1<sup>st</sup> Prototype Measurements Results

- Static Measurements

- Power Measurements

- Transient Measurements

- Comparison with other low-power 10 bit DACs

- Possible Improvements.

# Obsign of 2<sup>nd</sup> prototype – Improvements.

- Oircuit.

- Layout.

→ Ξ →

### Circuit improvements:

- New layout of the current sources matrix.

- Small improvements in amplifiers design.

- Decreased dimensions of linear current mirror sink and adds trimming.

#### Parameters of amplifiers in 2<sup>nd</sup> prototype:

### Circuit improvements:

- New layout of the current sources matrix.

- Small improvements in amplifiers design.

- Decreased dimensions of linear current mirror sink and adds trimming.

#### Parameters of amplifiers in 2<sup>nd</sup> prototype:

### Circuit improvements:

- New layout of the current sources matrix.

- Small improvements in amplifiers design.

- Decreased dimensions of linear current mirror sink and adds trimming.

#### Parameters of amplifiers in 2<sup>nd</sup> prototype:

# Design of 2<sup>nd</sup> prototype – Improvements.

### Circuit improvements:

- New layout of the current sources matrix.

- Small improvements in amplifiers design.

- Decreased dimensions of linear current mirror sink and adds trimming.

#### Parameters of amplifiers in 2<sup>nd</sup> prototype:

#### Circuit improvements:

- New layout of the current sources matrix.

- Small improvements in amplifiers design.

- Decreased dimensions of linear current mirror sink and adds trimming.

### Parameters of amplifiers in 2<sup>nd</sup> prototype:

|                                          | OTA N | OTA P | OP-AMP |

|------------------------------------------|-------|-------|--------|

| Gain [dB]                                | 96    | 93    | 136    |

| GBW [Hz] (10pF load)                     | 65k   | 130k  | 3M     |

| $PM\left[^{o} ight]\left(10pFload ight)$ | 96    | 90    | 70     |

| Total power cons. $[\mu W]$              | 5     | 10    | 72.5   |

### DAC Architecture Overview

- 2 10 bit Low–Power Small–Area Current–Steering DAC design.

- Specification

- Circuit Design.

- Layout

#### 3 1<sup>st</sup> Prototype Measurements Results

- Static Measurements

- Power Measurements

- Transient Measurements

- Comparison with other low-power 10 bit DACs

- Possible Improvements.

### Obsign of 2<sup>nd</sup> prototype – Improvements.

- Circuit.

- Layout.

→ Ξ →

Arch. Overview DAC Design Measurements New Design Circuit. Layout.

### Layout of $2^{nd}$ prototype – Improvements. 9 bit Current Sources Array.

Block Diagram of DAC Matrix Layout.

Arch. Overview DAC Design Measurements New Design Circuit. Layout.

# Layout of $2^{nd}$ prototype – Improvements. DAC Core.

Layout of  $2^{nd}$  prototype (385x530 $\mu$ m).

Dominik Przyborowski

Development of general purpose low-power small-area 10

### Summary

- $1^{st}$  prototype of 10 bit DAC is fully functional.

- Measurements results are generally in good agreement with simulations:

- Transfer curve LSB  $\simeq 2.6~[mV]$

- Integral Non–Linearity (INL)  $\simeq$  0.6 [LSB]

- Differential Non–Linearity (DNL)  $\simeq$  0.8 [LSB]

- Full scale settling time = 2  $[\mu s]$

- 1 LSB settling time < 500 [ns].

- Differential non-linearity is slightly higher than expected attributed to CS matrix layout.

- Improved design is completed and ready for submission.